光メモリは全光ルーティング・全光信号処理チップに不可欠の素子であり、特に前者は通信・データセンタの大容量ネットワークに加え、大規模集積CMOSチップ内/間光インタコネクトにも適用できる。光伝送の電子チップへの導入により、集積度が増すほど深刻になるデータ転送のコスト(電力・熱・配線面積・時間)を解決できると期待されている。我々は既にフォトニック結晶高Q値ナノ共振器により超小型光RAMの超低パワー(30 nW)動作を達成したが[1]、その高密度多ビット集積を可能とする技術は確立されていなかった。

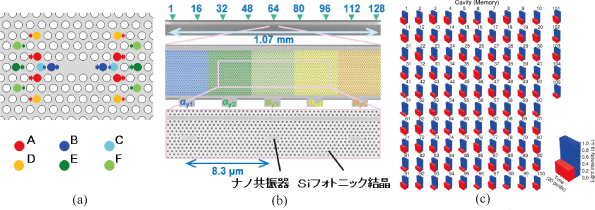

今回新たに3点欠陥ナノ共振器(L3)を採用し、多数の穴を規則的に調整する新設計によりQ値を10倍増加した[図1(a)][2]。同共振器の狭線幅、増強されたキャリアプラズマ双安定性、広いモード間隔により、各光RAMへの読出書込アクセスを波長多重により実現することが可能になり、128 bitのモノリシック集積光RAMを128個の直列L3配列と1本のサイド結合導波路による単純な構成で実現した[図1(b)][3]。各共振器の結晶周期を30 GHzの波長間隔を設定するため408 nmから424 nmまで0.125 nmずつ変調し、共振器間隔を20周期とした。128 bit集積光RAMチップの長さはわずか1.1 mmに収まった。この高精度L3共振器配列を含むSiフォトニック結晶チップを電子線リソグラフィにて作製した。各共振器(光RAM)の共振波長に合わせバイアス光を与えながら、set/resetパルスにより“1”と“0”の状態を切り替えることで、動作を確認した。図1(c)に示す通り、105ビットの光RAM動作が実証された。従来の数ビットからの画期的な大容量化と共に、全ビット合計30 mWという低消費電力化も達成した。さらに本技術をより高度なInP系埋込ヘテロ構造ナノ共振器に導入することで、より低消費電力で秒単位の時間で多ビット光RAM動作することを確認した[3]。

この精緻なナノフォトニクスの勝利により、1000ビット光RAMまでのモノリシック集積と、並列集積との組み合わせによる100万素子を1チップに集積した大規模光集積回路への道が拓かれた。