野崎謙悟 新家昭彦 松尾慎治* 須崎泰正* 瀬川徹* 佐藤具就*

高橋亮* 納富雅也

量子光物性研究部 *NTTフォトニクス研究所

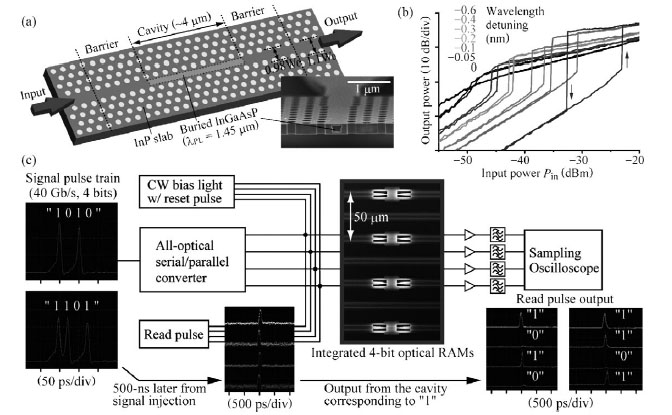

光信号を電気に変換せずに保持可能な光ランダムアクセスメモリ(光RAM)は、光ルータ等の光情報処理での利用が期待できるが[1]、サイズと消費パワーの制約により最も実現困難な光素子の一つであった。本研究では、フォトニック結晶(PhC)ナノ共振器におけるキャリア非線形効果を利用し、極めて低消費パワーの光RAM集積チップを実現した[2]。InP薄膜によるPhC中に微小なInGaAsP層を局所的に埋め込んだヘテロ構造[図1(a)]では,光とキャリアが共振器内に強く閉じ込められる。その結果、極めて低い光入力パワーでも光双安定現象が現れ[図1(b)]、光パルスの入射によってオン/オフの2状態を切り替えるメモリとして動作する。評価された最小メモリ動作パワーは30

nWと極めて低く、10 µm2 以下に収まる微小サイズも含め、大規模集積に適した光メモリ素子といえる。

実際にこのPhC光RAMを半導体チップ上に集積し、40 Gbit/s 光信号列のRAM動作を実証した[図1(c)]。4ビットの光信号列(1010または1101)は高速光シリアル/パラレル変換器により並列化され、個別に光RAMに書き込まれる。書込み動作の500

ns 後に読出し光パルスを入射させると、書込みがされた光RAMからのみ光パルスが出力することが確認された。すなわち、4ビット・40 Gbit/sの光信号列が500

nsだけメモリ保持されたことを示している。このようなナノ光デバイスを集積し協調動作させた例はこれまでになく、世界で初めての光RAM集積チップの実証である。

本研究は情報通信研究機構(NICT)の委託研究「全光パケットルータ実現のための光RAMサブシステムの研究開発」の一環として行われた。

[1] M. Notomi et al., IET Circuits Devices & Systems 5 (2011) 84.

[2] K. Nozaki et al., Nature Photon. 6 (2012) 248.

|

||

|