トランジスタを利用した単一電子・確率的情報処理回路

西口克彦 小野行徳 藤原 聡

量子電子物性研究部

情報処理回路の性能向上は、トランジスタの縮小化によって実現されてきた。しかし、トランジスタの誤動作を防ぐため電源電圧を下げることは困難とされており、トランジスタに流れる電流密度は増え続け、消費電力増加の大きな原因となっている。今回我々は、電流密度を究極的に単一電子レベルまで減少させ、単一電子のランダムな動きを高品質な乱数として利用した融通性のある確率的情報処理回路を実現した[1]。

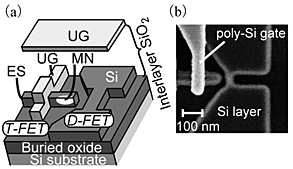

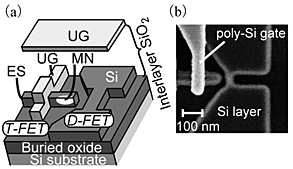

回路の基本素子はノンドープの絶縁膜上シリコンに形成した転送トランジスタ(T-FET) と電荷検出トランジスタ(D-FET) で構成される(図1)。T-FETは2層ゲート構造(UG,

LG) を有しており、UGでT-FET細線を反転して電子を誘起し、LGでエネルギーバリアを形成することにより、電子ソース(ES) と電荷蓄積ノード(MN)

を形成する。2層ゲートを利用した動作により、通常のトランジスタで問題となっている欠陥に起因した電流リークが発生しないため、ESからMNへのLGによる電流制御が単一電子レベルで可能となった[1,

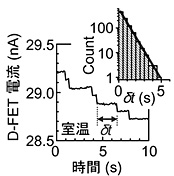

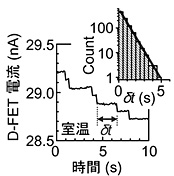

2]。MNに流れ込んだ単一電子は、MNと容量結合したD-FETの電流変化量で検出する(図2)。素子構造、動作条件の最適化により室温での単一電子検出を実現した[3]。単一電子がMNに注入されるタイミングδtの分布を評価することにより、単一電子の振る舞いがポアソン過程であることを確認した。これは同時にトランジスタのショットノイズをリアルタイムでモニタしたことを意味している。

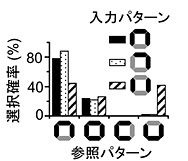

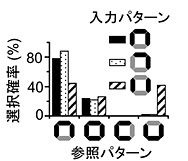

ポアソン過程である単一電子のランダムな振る舞いは高品質な乱数として利用できる。今回はパターン認識回路に用いることで融通性のある回路動作を実現した。入力パターンと最も似ている参照パターンを選択する回路で、図3に示すように入力パターンとの類似性に応じた確率で参照パターンを選択する。また、この選択確率の分布はLGにより制御可能で、入力パターンが参照パターンと異なる場合でも、もっともらしい参照パターンを効率的に選択することが可能となる。これらの特徴を利用することで人間のように融通の利く回路動作が可能となり、パターン認識のみでなくデータ分類や最適化問題など多くのデータを扱う応用面などで高効率な動作が期待できる。

[1] K. Nishiguchi et al., Appl. Phys. Lett. 92 (2008) 062105.

[2] K. Nishiguchi et al., IEEE Electron Device Lett. 28 (2007) 48.

[3] K. Nishiguchi et al., Jpn. J. Appl. Phys. 47 (2008) 8305.

|

|

|

|

|

| 図1 |

シリコン・トランジスタを組み合わせた素子構造 (a)鳥瞰図 (b)電子顕微鏡写真。 |

|

|

| 図2 |

単一電子電流のリアルタイム・モニタ。挿入図:単一電子がMNに注入されるタイミングδt のヒストグラム。 |

|

|

| 図3 |

融通性のあるパターン認識回路特性。入力パターンに類似した参照パターンを選択。 |

|

【前ページ】 【目次へもどる】 【次ページ】