微小な埋め込みヘテロ構造を含むフォトニック結晶InGaAs光ディテクタ

現在、CMOSチップ間光リンクやオンチップ光処理に向けたチップ内光リンクの研究が展開されており、CMOSと融合可能な高速・高効率なフォトディテクタ(PD)の実現が要求されている。pin接合をもつPDでは、その接合容量を著しく低減できれば、RC時定数を劣化させることなく高い負荷抵抗を連結させることができる。これにより、熱雑音低下による高感度化、ならびに出力電圧の増加が可能となり、結果として光源を含めた光リンク全体の消費電力抑制が期待される。それに加え、理想的には、電気増幅器を除いてもCMOS駆動が可能な“レシーバレスPD”を構成することも期待できる。我々はこれらの目的に向けて、微小なナノ構造PDの実現を目指している。

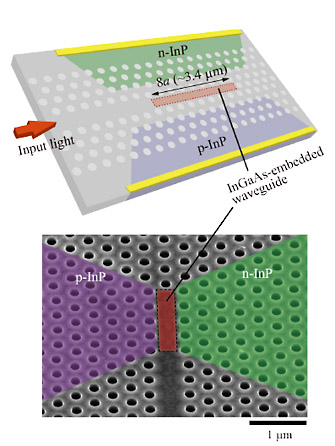

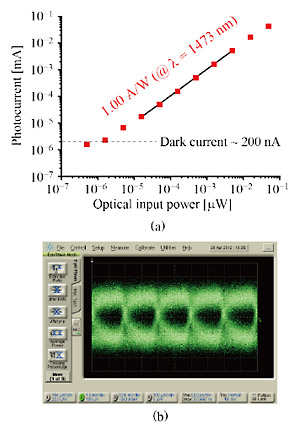

強い光閉じ込めが可能なフォトニック結晶(PhC)導波路では、PD全長が短くても高い量子効率が得られるため、pin接合長もまた短くでき、微小容量化に向いている。図1はPhC導波路型pin-PDの構造図とSEM写真である[1]。InPスラブのPhC導波路中に微小なInGaAs吸収層(長さ約3.4 µm)が埋め込まれており、その両サイドへのZn拡散,Siイオン注入により横方向pin接合が形成されている。逆バイアス電圧印可下(–1 V)において,PhC導波帯域内の波長のCW光を入力したときの光電流を図2(a)に示す。このときの光-電流変換効率は約1 A/Wであり、十分高い効率が得られた。すなわち埋め込み界面でのキャリア捕獲や非発光再結合などの悪影響がなく効率的に光電流の生成がなされていることを示す。図2(b)は、231–1の疑似ランダム光信号入力に対するアイパターンであり、ビットレート10 Gb/s程度の高速応答が得られた。今後、RC時定数の低減による更なる高速化とともに、負荷抵抗の連結によるオンチップ光-電圧変換も可能と考えられ、将来のチップ内光リンクに向けた低エネルギーかつ微小な光受信器の実現が期待される。

- [1]

- K. Nozaki, S. Matsuo, K. Takeda, T. Sato, E. Kuramochi, and M. Notomi, Opt. Express 21 (2013) 19022.

|

|

|

|