鈴木恭一 原田裕一 前田文彦* 小野満恒二 山口 徹 村木康二

量子電子物性研究部 *機能物質科学研究部

InAs/AlGaSbヘテロ構造は室温で高い移動度を持つことから、数十年来、高周波FET等の高速電子デバイスとして期待されてきた。しかしながら、デバイス応用に際してはAlGaSb障壁層やGaSbキャップ層の絶縁が不十分なため、ゲート制御に困難があった。これを克服するため、種々の方法でキャップ層とゲート金属間に絶縁膜を形成する試みがなされてきた。特に近年開発された原子層堆積法(ALD)は、様々な物質表面に高誘電率の絶縁酸化膜を薄く均一に形成することが可能であり、InAs/AlGaSbヘテロ構造への適用が期待されている[1、2]。

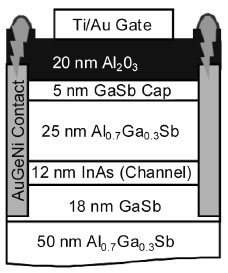

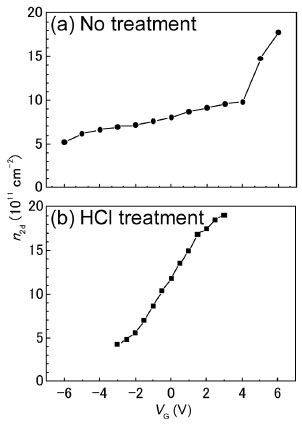

従来、InAs/AlGaSb系でALDゲート絶縁膜を形成する場合、GaSbキャップ層表面の自然酸化膜や絶縁膜との界面に生じる欠陥が電子トラップとなり、ゲート電界が打ち消され、効率が低下する問題があった。今回我々は、薄い塩酸による短時間の表面処理によって、ALDによるAl2O3絶縁膜形成後の電子トラップ密度を大幅に低減することに成功した(図1)[3]。これにより、InAs/GaSbヘテロ構造において、線形性に優れ、高効率な電子濃度制御が可能となった(図2)。

[1] J. E. Crowell, J. Vac. Sci. Technol. A 21 (2003) S88.

[2] I. J. Gelfand, S. Amasha, D. M. Zumbuhl, M. A. Kastner, C. Kadow, and

A. C. Gossard, Appl. Phys. Lett. 88 (2006) 252105.

[3] K. Suzuki, Y. Harada, F. Maeda, K. Onomitsu, T. Yamaguchi, and K. Muraki, Appl. Phys. Express 4 (2011) 125702.

|

|

|||||

|

|