西口克彦 小野行徳 藤原 聡

量子電子物性研究部

キャパシタからなるメモリノード(MN)にデータを電荷として保持するDRAM(Dynamic

Random Access Memory)はメモリ素子の代表格であり、その微細化により大容量化が進められてきた。しかし、電荷を蓄積するMN容量を小さくすると蓄積電荷信号がノイズに埋もれてしまうため、さらにMN容量を小さくすることが困難になっている。このため、素子微細化と同時にMN容量を確保しなければならず、複雑なMN構造や新たな材料を利用することが求められ複雑な作製方法やコスト上昇に繋がっていた。

これを解決する素子の1つがゲインセル・メモリであり、MNの蓄積電荷信号を直近のトランジスタで増幅することで、小さなMN容量でもメモリ動作が可能となる。これにより、素子構造の簡素化だけでなく、情報処理回路との混載化による回路性能の向上が期待できる。しかし、MN容量を小さくすると蓄積電荷量も減少するので、データ保持時間が短くなる(1秒以下)という問題が実用化を妨げていた。これは、MN部に形成されたpn接合部で電子-正孔ペアが発生することが原因であった。この問題は通常のDRAMでも共通の課題であり、その対策として常にデータの再書き込み(リフレッシュ)を行っているため、消費電力の上昇のみでなくメモリ容量の利用効率を下げていた。

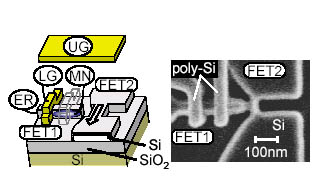

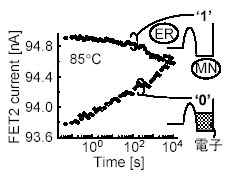

今回我々は、pn接合の無いMN構造によりデータ保持時間の長いゲインセル・メモリを実現した[1]。図1は素子構造を示しており、ノンドープ絶縁膜上シリコン(SOI)に形成した電荷転送用トランジスタ(FET1)と検出用トランジスタ(FET2)で構成される。これらの上部を覆う上層ゲート(UG)でFET1のアンドープSOIチャネルを反転させ、下層ゲート(LG)でFET1をOFFにすることでFET1チャネルの先端に数十aF程度のMNを形成する。FET1をON・OFFして電子溜め(ER)-MN間で電子蓄積(データ‘0’)・放出(‘1’)を行い、MNと容量結合したFET2の電流変化によって蓄積電子信号を読み出す。従来のDRAMではFET1とMNの接合部にpn接合を形成しているが、本素子ではpn接合をノンドープチャネルの反転層で置き換えているため、85℃で104秒のデータ保持特性が得られた(図2)。

本素子により、リフレッシュ動作の頻度を数桁下げることが可能となり、それによる低消費電力化が可能となる。また、素子作製方法はSOI・LSI作製技術をベースとしているので、情報処理回路との混載化も期待できる。

[1] K. Nishiguchi, et al., IEEE Electron Device Lett. 28 (2007) 48.

|

|

|||||

|

|