永瀬雅夫 日比野浩樹* 影島博之 山口浩司

量子電子物性研究部 *機能物質科学研究部

グラフェンはその優れた電子物性に注目が集まり研究が盛んになっている。特にSiC基板上のエピタキシャルグラフェンは、従来の半導体プロセスとの互換性が高いため、Beyond CMOS向けの電子材料として有望である。近年、低エネルギー電子顕微鏡 (LEEM) を用いたSiC上グラフェンの高分解能層数同定技術が確立された[1]。この技術を用いることにより数層グラフェンの層数、および、形態を制御することが可能となった。我々が取り組んでいるグラフェン・シングルレイヤエレクトロニクスの実現に向けての次の重要な課題が、グラフェン成長後の電気的な特性の顕微的な評価である。この目的のため、これまでに走査プローブ顕微鏡 (SPM) のSiカンチレバー上に集積化した数種類のナノツールを開発してきた[2]。本稿では、ナノツールの1つである集積化ナノギャッププローブによるグラフェンのナノオーダ局所導電率の計測結果について述べる[3]。

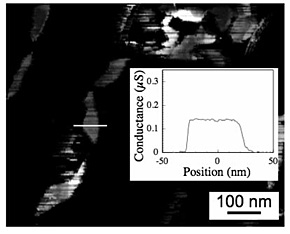

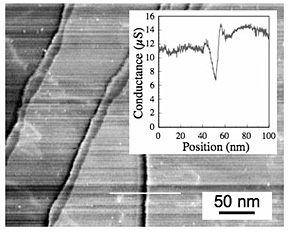

図1は、ナノグラフェンの面内導電率像、および、個別のナノ構造の導電率プロファイルである。この試料のグラフェンの被覆率はLEEMの観察結果を用いて注意深く制御してある。集積化ナノギャッププローブによる局所導電率の計測結果からこれらのナノグラフェンは1層と2層からなることが分かった。計測に用いたナノツールでは30 nmのナノギャップに隔てられた2つのPt電極をカンチレバー上に集積化しているため、絶縁基板上のナノ構造であってもリソグラフィ等のプロセス工程を経ることなく電気特性の取得が可能である。図2はSiC上に均一に成長した2層グラフェンの局所導電率像である。LEEM観察からは2層グラフェンの単結晶ドメインがステップを越えて形成されていることが確認されている。一方、図2の導電率像、および、導電率プロファイルでは試料表面のステップ構造に由来する導電率低下が明瞭に観察される。ナノ分解能を有する導電率マッピング技術は、カーボンベースのシングルレイヤエレクトロニクスの実現に向けた有用な技術であることを示すことができた。

なお本研究の一部は科研費 (19320085、20246064) の助成を受けて行われた。

[1] H. Hibino et al., Phys. Rev. B 77 (2008) 075413.

[2] M. Nagase et al., Jpn. J. Appl. Phys. 46 (2007) 5639.

[3] M. Nagase et al., Nanotechnol. 19 (2008) 495701.

|

|

|||||

|

|