ゲートオーバラップをもつGate-All-Around InAsナノワイヤFET

結晶成長により得られる半導体ナノワイヤは、次世代ナノデバイスの構成材料として近年注目を集めている。特にInAsは高易動度のナローギャップ材料であることに起因して、これを伝導

チャネルとする電界効果トランジスタ(FET)においては大きな駆動電流が得られる。さらに、ナノワイヤをゲート電極で完全に取り囲んだGate-All-Around (GAA) 構造を採用するとゲート電界による電流制御性が改善し、高ON/OFF比のFETが実現できると期待される。今回我々は、ゲート電極を2段階で形成することにより横型GAA InAsナノワイヤFETを作製し、特にゲート電極がソース・ドレイン電極とオーバラップした構造において、ナノワイヤFETとしてトップクラスのON特性を実現した[1]。

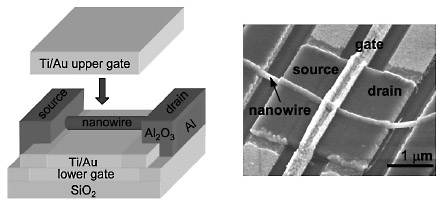

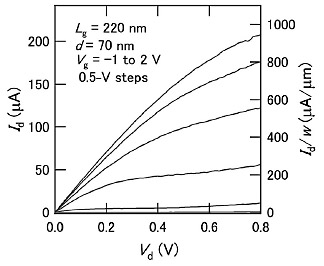

図1は作製したInAsナノワイヤFETの模式図と走査型電子顕微鏡像である。成長後のナノワイヤ表面は原子層堆積法(ALD)を用いて、厚み6 nmのAl2O3絶縁膜で被覆しておく。デバイス作成用のSi基板上には図1のような段つき断面形状を有する下層ゲート電極を形成しておき、この上にナノワイヤを転写する。ナノワイヤ両端部分にEBリソグラフィによって電極パタンを形成し、アルゴンクリーニングによってナノワイヤ表面の酸化膜を除去後、ナノワイヤを大気に曝さずにAlを蒸着し、低接触抵抗のソース・ドレイン電極を形成した。ソース・ドレイン電極の表面は酸化してAl2O3絶縁膜にしておき、この上から上層ゲート電極をソース・ドレイン電極にオーバラップするように蒸着すると、ナノワイヤが上下層のゲート電極に挟まれたGAA構造が完成する。図2は、室温におけるドレイン電流(Id)-ドレイン電圧(Vd)特性をゲート電圧Vgを変えながら測定した出力特性で、閾値0.39 Vのn型FETとなっている。ここで、ナノワイヤチャネルの直径dは70 nm、ゲート長Lgは220 nmである。ドレイン電流をナノワイヤの周長w = πdで規格化した値も同時に示す。ドレイン電圧0.5 Vにおける規格化相互伝導度gm/w は0.55 S/mmと、均一のInAsナノワイヤをチャネルとするFETとしてはこれまでの最高値となっている。このような優れたON特性は、GAA構造によるゲート電界制御性の改善とゲートオーバラップ構造による寄生抵抗の低減を同時に達成したことによる。

- [1]

- S. Sasaki,G. Zhang, K. Tateno, H. Suominen, Y. Harada,S. Saito,A. Fujiwara, T. Sogawa, and K. Muraki, Appl. Phys. Lett. 103 (2013) 213502.

|

|

|

|