極低温におけるシリコン単電子転送素子の精度評価

単電子転送は1個の電子を正確に操作する技術であり、超低消費電力素子や電流標準等への応用が期待されている。応用へ向け、転送エラーレート10–8以下の高い転送精度が必要である。これまで我々は、シリコン単電子転送素子の転送精度絶対評価を報告したが、比較的高温(T = 17 K)での測定であったため、エラーレートは10–2程度であった[1]。今回は転送精度絶対評価を極低温(T = 30 mK)で行い、10–4程度のエラーレートを達成した。さらに、理論的にはエラーレートは10–8オーダーまで下がる可能性があることを確認した[2]。

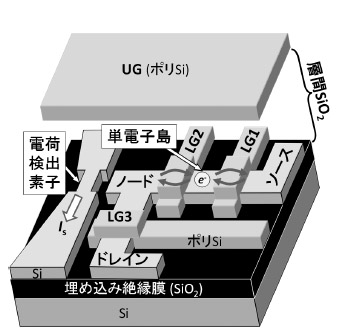

図1に素子の概略図を示す。Silicon-on-insulator基板上にLG1、LG2、LG3をゲート電極とする3つの細線トランジスタからなる単電子転送素子と、UGをゲート電極とする細線トランジスタからなる電荷検出素子を作製した。LG3に正電圧を、LG1とLG2にパルス電圧を印加すると、LG1-LG2間の単電子島を介してソース-ドレイン間に転送電流が流れる。さらに、LG3に負電圧を印加しノードを形成した状態で、ソースにパルス電圧を印加すると、単電子をノード-ソース間で往復させることができる。その際のノードの電子数変化を、電荷検出素子に流れる電流ISの変化で読み取ることで転送エラーを評価した。

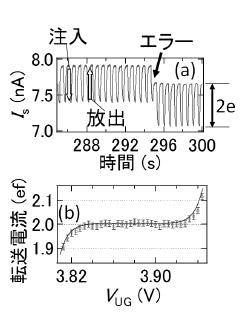

本実験では2つの電子を転送する際の転送エラーを評価した。図2(a)に2電子を往復させた際のISの変化を示す。急峻なISの増減は2電子のノードへの放出・注入に対応する。図に示すようなエラーをカウントしエラーレートを見積もった結果、10–4程度と以前より2桁改善した。エラーの原因はパルス電圧に起因する素子の実効温度(Teff)上昇であることも判明した。さらに、転送電流の理論的フィッティング(図2(b))よりエラーレートの下限値を見積もった。パルス電圧振幅を減少させて素子の実効温度を降下させると、転送機構が変化し、それに伴いエラーレートの下限値も下がっていくことがわかった。実効温度が低い領域(Teff ~ 5 K)では、10–8オーダーの極めて低いエラーレートとなる可能性が示唆された。

本研究の一部は最先端・次世代研究開発支援プログラムの助成を受けて行われた。

- [1]

- G. Yamahata, K. Nishiguchi, and A. Fujiwara, Appl. Phys. Lett. 98 (2011) 222104.

- [2]

- G. Yamahata, K. Nishiguchi, and A. Fujiwara, Phys. Rev. B 89 (2014) 165302.

|

|

|

|